OSHChip V1.0 SWD 2x2 Adapter

Description

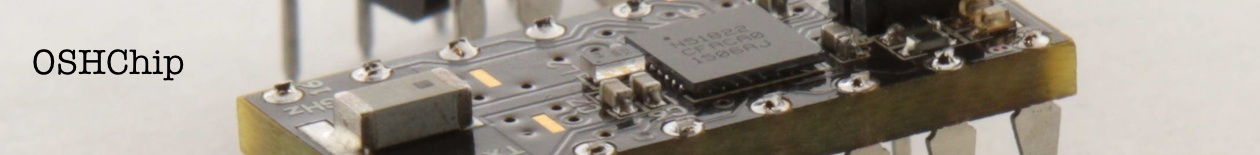

The programmer/debugger for OSHChip V1.0, OSHChip_CMSIS_DAP V1.0 has a standard SWD interface header with 10 pins (2 by 5) and spacing in X and Y of 0.050” (1.27mm). A matching ribbon cable with keyed female IDC connectors is supplied with each OSHChip_CMSIS_DAP V1.0.

OSHChip V1.0 has a small 4 pin connector on the top side that is used for programming the Flash memory, and can also be used for debugging. The 4 pins are the minimal pins needed to implement the ARM Cortex SWD interface.

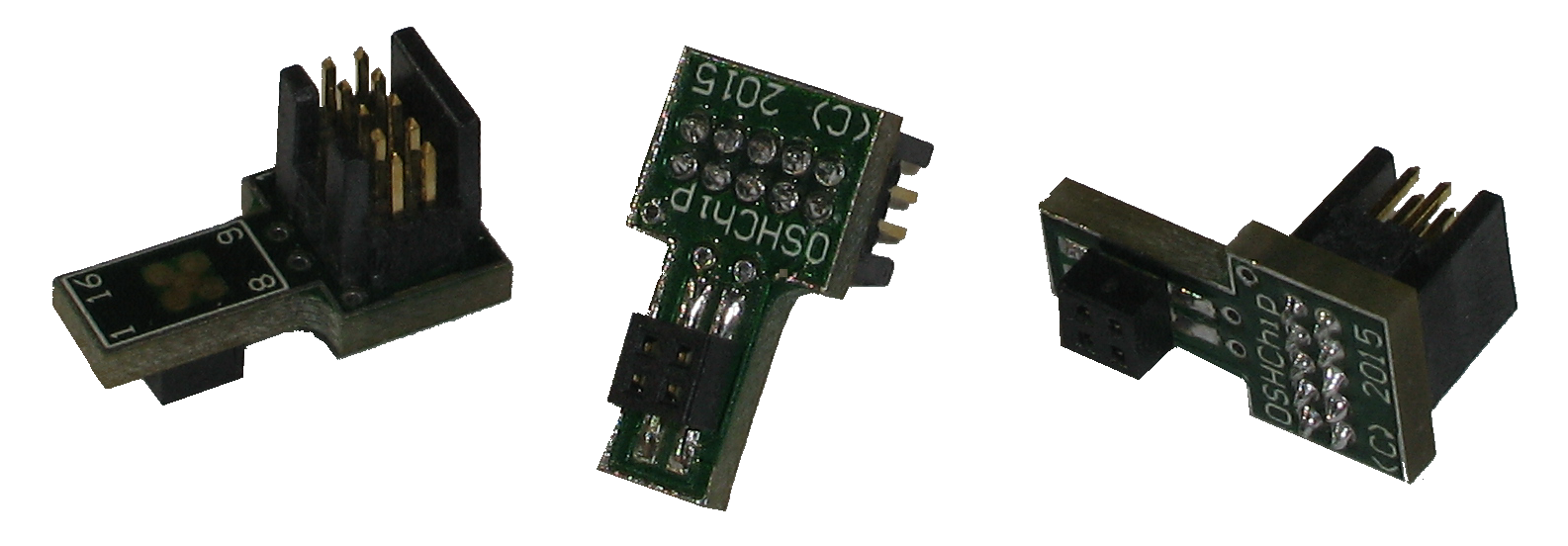

The OSHChip SWD 2x2 Adapter provides a compact conversion from the 10 pin standard to the 4 pin connector on OSHChip.

Programming/Debugging cable orientation

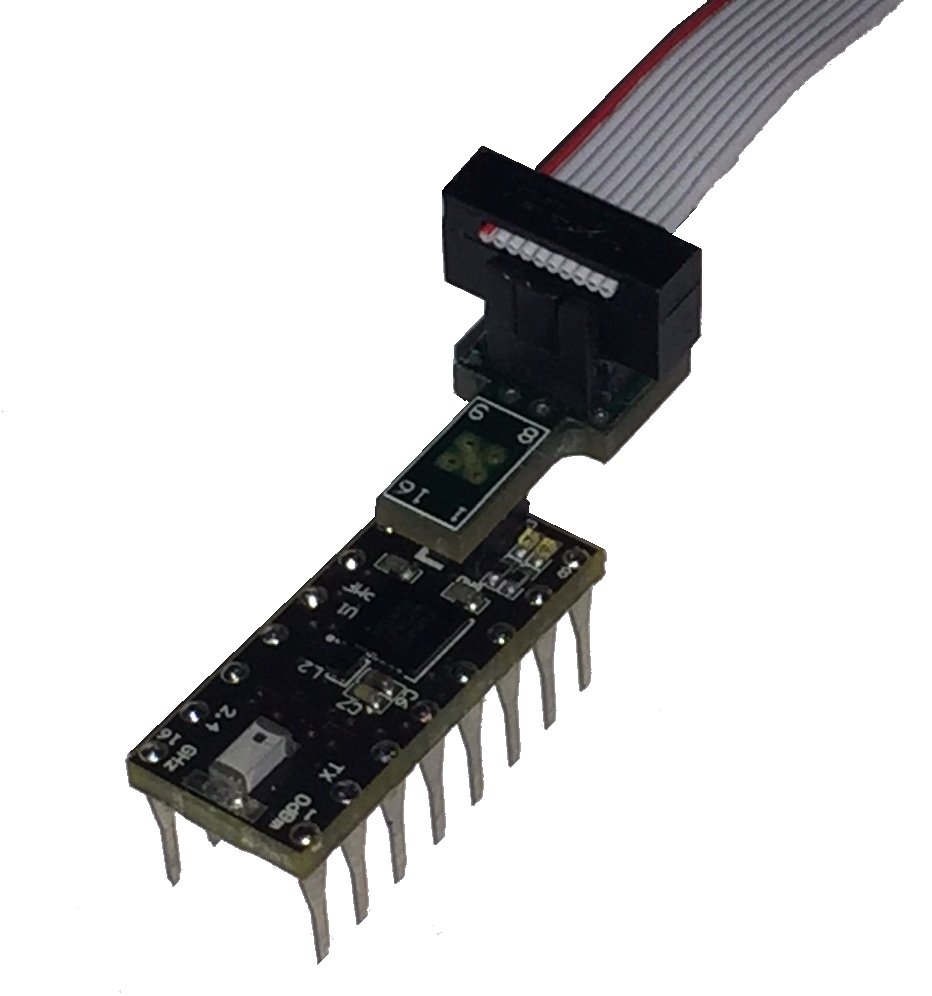

Programming cable, adapter, and OSHChip

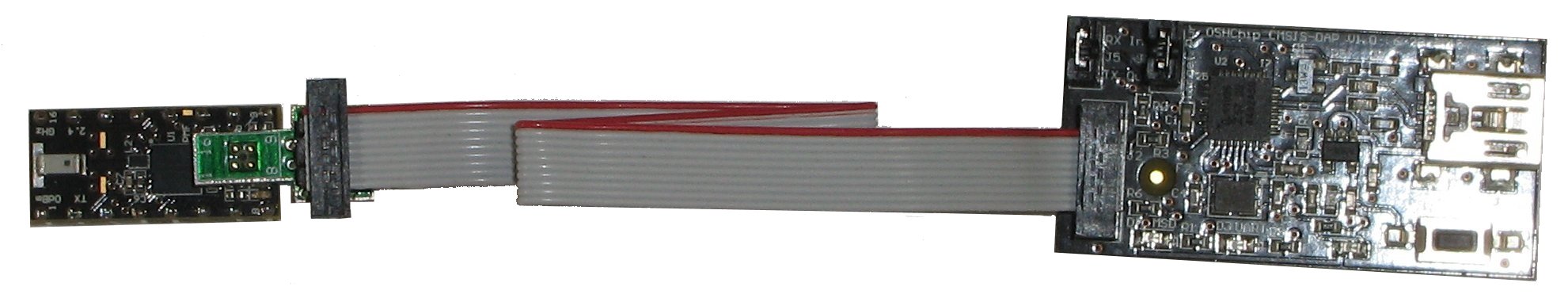

OSHChip, Adapter, Cable, and OSHChip_CMSIS_Dap